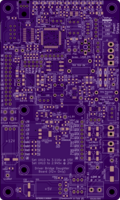

Dual Resonance Solid-State Tesla Coil Driver V5.1

author: dewhisna

2 layer board of 3.00 x 5.00 inches (76.2 x 127.0 mm)

Uploaded:

June 13, 2023

Shared:

June 13, 2023

Total Price:

$75.00

Driver board for a Dual-Resonance Solid-State Musical Tesla Coil. This version is a minor update to the DRSSTCDriver V5 design. It uses a CPLD for adding freewheeling support. For freewheeling, it requires a V2 Driver Bridge daughter board (either: UCC37322D V2 or FDD8424H V2 ).

This board fixes the OPF2412T footprint errata. It also replaces the pulse-width-limiter (PWL) circuit with a new LTC6993-2 variant. The original PWL required as long (or longer) off-time for the fiber optic pulse-width as the on-time, which doesn’t work well for certain types of interrupter drive (like music, for example). It only worked well for BPS (or bangs per second) drive. This version also adds a new configuration jumper for enabling/disabling the feedback delay loop. And it adds an enable/disable jumper for the HVFault input, along with an additional filter cap for that input. Additionally, several component values were tweaked with numbers better suited for most coils.

See also the DRSSTC Data Acquisition Board V3 for a matching data acquisition board for this driver board.

ERRATA:

- UVLO issue : The output of U9 (LM8365BALMF27) Vlo level is too high to properly trigger the CPLD Schmitt-trigger input due to the Vf drop of D14 and with the low impedance of R53 and R19, and is even worse when the TCDAQ is present as it adds to the low impedance of R53. Use a MBR0530 Schottky diode for D14 in place of the LL4148. Use a 100K resistor for R19 in place of the 1K and use a 10K resistor for R53 in place of the 1K.

Driver board for a Dual-Resonance Solid-State Musical Tesla Coil. This version is a minor update to the DRSSTCDriver V5 design. It uses a CPLD for adding freewheeling support. For freewheeling, it requires a V2 Driver Bridge daughter board (either: UCC37322D V2 or FDD8424H V2 ).

This board fixes the OPF2412T footprint errata. It also replaces the pulse-width-limiter (PWL) circuit with a new LTC6993-2 variant. The original PWL required as long (or longer) off-time for the fiber optic pulse-width as the on-time, which doesn’t work well for certain types of interrupter drive (like music, for example). It only worked well for BPS (or bangs per second) drive. This version also adds a new configuration jumper for enabling/disabling the feedback delay loop. And it adds an enable/disable jumper for the HVFault input, along with an additional filter cap for that input. Additionally, several component values were tweaked with numbers better suited for most coils.

See also the DRSSTC Data Acquisition Board V3 for a matching data acquisition board for this driver board.

ERRATA:

- UVLO issue : The output of U9 (LM8365BALMF27) Vlo level is too high to properly trigger the CPLD Schmitt-trigger input due to the Vf drop of D14 and with the low impedance of R53 and R19, and is even worse when the TCDAQ is present as it adds to the low impedance of R53. Use a MBR0530 Schottky diode for D14 in place of the LL4148. Use a 100K resistor for R19 in place of the 1K and use a 10K resistor for R53 in place of the 1K.