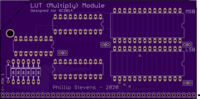

RC2014 LUT (Multiply) Module

author: feilipu

4 layer board of 3.91 x 1.98 inches (99.4 x 50.2 mm)

Uploaded:

February 15, 2020

Shared:

February 15, 2020

Total Price:

$77.30

The RC2014 Z80 needed to have a fast multiply, and this is it.

design discussion on RC2014 forum

This 128kByte look-up table (LUT) Module allows the RC2014 to directly look up a 16-bit result at a 16-bit address.

The first application for the LUT Module is for an 16-bit result from a 8-bit x 8-bit multiply. It takes 61 clock cycles to return the result, and this is approximately 5 times faster than a shift-add multiply and 2.5 times faster than the best table multiply software routine.

The LUT Module can also hold other tables, including SINE or LOG / LN to 16-bit accuracy, CRC results, or other pre-calculable tables that need to be read quickly.

To multiply Register H by Register L, and return the result in HL, preserving all registers except BC.

mul_hl:

ld b,h ; 4 multiplier to B

ld c,0x40 ; 7 operand latch address

out (c),l ; 12 multiplier from B, multiplicand from L

in l,(c) ; 12 result LSB to L

inc c ; 4 result MSB address

in h,(c) ; 12 result MSB to H

ret ; 10

The RC2014 Z80 needed to have a fast multiply, and this is it.

design discussion on RC2014 forum

This 128kByte look-up table (LUT) Module allows the RC2014 to directly look up a 16-bit result at a 16-bit address.

The first application for the LUT Module is for an 16-bit result from a 8-bit x 8-bit multiply. It takes 61 clock cycles to return the result, and this is approximately 5 times faster than a shift-add multiply and 2.5 times faster than the best table multiply software routine.

The LUT Module can also hold other tables, including SINE or LOG / LN to 16-bit accuracy, CRC results, or other pre-calculable tables that need to be read quickly.

To multiply Register H by Register L, and return the result in HL, preserving all registers except BC.

mul_hl:

ld b,h ; 4 multiplier to B

ld c,0x40 ; 7 operand latch address

out (c),l ; 12 multiplier from B, multiplicand from L

in l,(c) ; 12 result LSB to L

inc c ; 4 result MSB address

in h,(c) ; 12 result MSB to H

ret ; 10